...

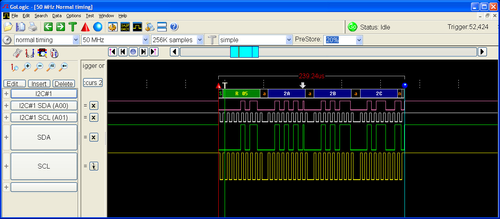

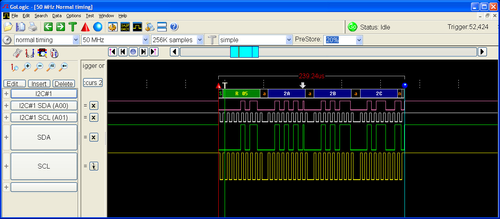

The figure below illustrates a "read" transaction. The

| Include Page |

|---|

| _def_chip_eterna |

|---|

| _def_chip_eterna |

|---|

|

chip starts by sending a header byte containing the address of the slave to read from (here

0x05), as well as the "read" bit. The

| Include Page |

|---|

| _def_chip_eterna |

|---|

| _def_chip_eterna |

|---|

|

chip (the I2C master) then sends a clock signal which the slave uses to time the bits it sends back over the SDA line to the master. In this case, the slave returns the bytes

0x2A ,

0x2B,

0x2C.

| Note |

|---|

Some I2C device documentation will describe the 7-bit address as though it is already shifted left to accommodate the read/write bit (which is b0 of the address word). The OCSDK driver expects the 7-bit address to be right justified. E.g. The Sensirion SHT21 documentation gives the device address (in binary) as 1000 000 - the driver is expecting to see 0x40, not 0x80. |

The 02-i2c Sample Application

...